## OPERATING SYSTEMS FOR FAR OUT MEMORIES

## DANIEL BITTMAN

June 2023 – v. 1.1

Daniel Bittman Operating Systems for Far Out Memories Copyright © June 2023

COLOPHON

The author battled LATEX for typesetting using an unabashedly strong influence from Aaron Turon's dissertation<sup>1</sup> as inspiration for formatting. The document uses a modified classicthesis by André Miede. A variety of fonts are used, but there is no Arial to be found.

<sup>1</sup> http://aturon.github.io/ academic/turon-thesis.pdf

## CONTENTS

| I                            | Prel                    | ude                                         |  |  |  |  |

|------------------------------|-------------------------|---------------------------------------------|--|--|--|--|

| 1                            | Introduction 3          |                                             |  |  |  |  |

| 2 Far Out Memory Hierarchies |                         |                                             |  |  |  |  |

|                              | 2.1                     | Memory and Compute                          |  |  |  |  |

|                              |                         | 2.1.1 Distribution                          |  |  |  |  |

|                              |                         | 2.1.2 Memory Density                        |  |  |  |  |

|                              |                         | 2.1.3 The Heterogeneity of Memory           |  |  |  |  |

|                              | 2.2                     | Some Kind of Model                          |  |  |  |  |

|                              | 2.3                     | So, What Does This All Mean?                |  |  |  |  |

| 3                            | The Demands of Software |                                             |  |  |  |  |

|                              | 3.1                     | The Old Ways and "Systems Programming" 13   |  |  |  |  |

|                              |                         | 3.1.1 The Context Problem                   |  |  |  |  |

|                              | 3.2                     | Retrofitting POSIX?                         |  |  |  |  |

|                              | 3.3                     | Remote Procedure Calls                      |  |  |  |  |

|                              | 3.4                     | So, What Does This All Mean (part 2)?       |  |  |  |  |

|                              |                         |                                             |  |  |  |  |

| II                           |                         | ata-Centric OS                              |  |  |  |  |

| 4                            |                         | Data-Centric Approach 25                    |  |  |  |  |

|                              | 4.1                     | An Opportunity Arises 25                    |  |  |  |  |

|                              | 4.2                     | A Design Space                              |  |  |  |  |

|                              | 4.3                     | Twizzler: A Point in the Design Space    28 |  |  |  |  |

|                              | 4.4                     | A Historical Look                           |  |  |  |  |

|                              |                         | 4.4.1 Classifying Operating Systems         |  |  |  |  |

|                              | 4.5                     | Conclusion                                  |  |  |  |  |

| 5                            | AG                      | lobal Address Space 35                      |  |  |  |  |

|                              | 5.1                     | Memory Objects                              |  |  |  |  |

|                              | 5.2                     | Object IDs                                  |  |  |  |  |

|                              | 5.3                     | Mapping Back to Virtual Memory 38           |  |  |  |  |

|                              | 5.4                     | A Logical Address Space                     |  |  |  |  |

|                              | 5.5                     | Conclusion                                  |  |  |  |  |

| 6                            |                         | riant References 43                         |  |  |  |  |

|                              | 6.1                     | Implementation 43                           |  |  |  |  |

|                              | 6.2                     | Evaluation                                  |  |  |  |  |

|                              |                         | 6.2.1 Case Study: Key-Value Store           |  |  |  |  |

|                              |                         | 6.2.2 Case Study: Red-Black Tree            |  |  |  |  |

|                              |                         | 6.2.3 Porting SQLite                        |  |  |  |  |

|                              |                         | 6.2.4 Case Studies Discussion               |  |  |  |  |

|                              |                         | 6.2.5 Storage Overhead                      |  |  |  |  |

|                              |                         | 6.2.6 Performance                           |  |  |  |  |

|     | 6.3                            | Conclusion                                       |  |  |  |

|-----|--------------------------------|--------------------------------------------------|--|--|--|

| 7   | Twizzler: An Implementation 59 |                                                  |  |  |  |

|     | 7.1                            | Object Services                                  |  |  |  |

|     |                                | 7.1.1 Copy-From                                  |  |  |  |

|     |                                | 7.1.2 Creation                                   |  |  |  |

|     |                                | 7.1.3 Deletion                                   |  |  |  |

|     |                                | 7.1.4 External Paging                            |  |  |  |

|     | 7.2                            | Dealing with Ephemera 61                         |  |  |  |

|     |                                | 7.2.1 Views 61                                   |  |  |  |

|     |                                | 7.2.2 Threads                                    |  |  |  |

|     |                                | 7.2.3 Program Instancing 63                      |  |  |  |

|     | 7.3                            | Security                                         |  |  |  |

|     |                                | 7.3.1 Security Contexts and Page Tables          |  |  |  |

|     |                                | 7.3.2 Virtualization Hardware                    |  |  |  |

|     | 7.4                            | POSIX Compatibility                              |  |  |  |

|     |                                | 7.4.1 Porting to Twizzler                        |  |  |  |

|     |                                | 7.4.2 Twix System Call Overhead                  |  |  |  |

|     | 7.5                            | Conclusion                                       |  |  |  |

| 8   | Prog                           | ramming Model 69                                 |  |  |  |

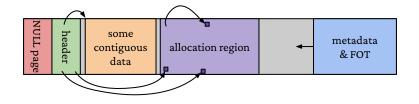

|     | 8.1                            | Object Layout                                    |  |  |  |

|     | 8.2                            | The Flipside         71                          |  |  |  |

|     | 8.3                            | Crash Consistency                                |  |  |  |

|     | 8.4                            | Memory Safety and Lifetimes                      |  |  |  |

|     |                                | 8.4.1 Object Types, Persistence, and Lifetime 74 |  |  |  |

|     |                                | 8.4.2 Object Ties and Logical Lifetime           |  |  |  |

|     |                                | 8.4.3 Safe Allocation                            |  |  |  |

|     | 8.5                            | Conclusion                                       |  |  |  |

|     | -                              |                                                  |  |  |  |

| III | Epilo                          | gue                                              |  |  |  |

| 9   | Conc                           | lusion 83                                        |  |  |  |

|     | 9.1                            | To Look Ahead                                    |  |  |  |

|     |                                | 9.1.1 Future Models                              |  |  |  |

|     |                                | 9.1.2 Future Research                            |  |  |  |

|     | 9.2                            | Looking Behind 86                                |  |  |  |

|     | 9.3                            | Final Remarks                                    |  |  |  |

|     | 1                              | and in                                           |  |  |  |

| IV  | Appe                           |                                                  |  |  |  |

| Α   |                                | her flippant appendix 91                         |  |  |  |

|     | A.1                            | Introduction                                     |  |  |  |

|     | A.2                            | Non-volatile Memory and Bit Flips                |  |  |  |

|     |                                | A.2.1 Optimizing for Memory Technologies 93      |  |  |  |

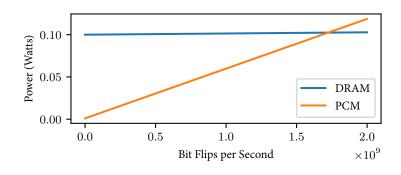

|     |                                | A.2.2 Power Consumption of PCM and DRAM 93       |  |  |  |

|     |                                | A.2.3 Wear-out                                   |  |  |  |

|     | A.2.4 Reducing Impact of Bit Flips in Non-volatile |                                |  |

|-----|----------------------------------------------------|--------------------------------|--|

|     |                                                    | Memory                         |  |

| A.3 | Reduc                                              | ing Bit Flips in Software      |  |

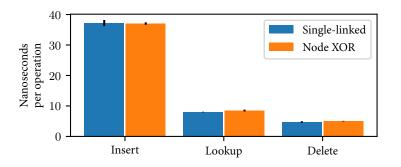

|     | A.3.1                                              | XOR Linked Lists               |  |

|     | A.3.2                                              | XOR Hash Tables         97     |  |

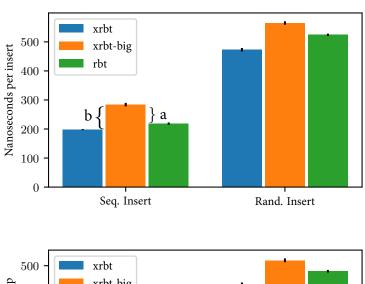

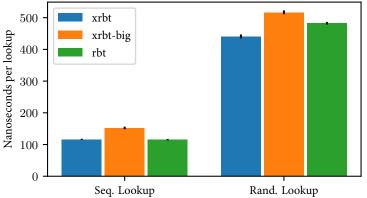

|     | A.3.3                                              | XOR Red-Black Trees         98 |  |

|     | A.3.4                                              | Stack Frames                   |  |

| A.4 | Memo                                               | ry Characteristics Results     |  |

|     | A.4.1                                              | Experimental Methods           |  |

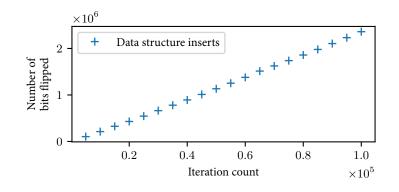

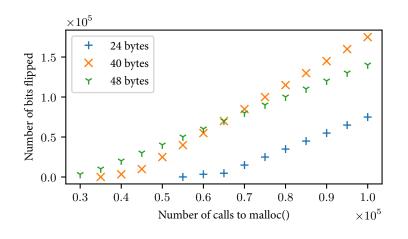

|     | A.4.2                                              | Calls to malloc                |  |

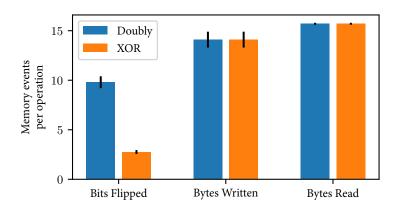

|     | A.4.3                                              | XOR Linked Lists               |  |

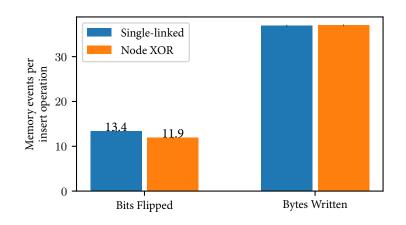

|     | A.4.4                                              | XOR Hash Tables                |  |

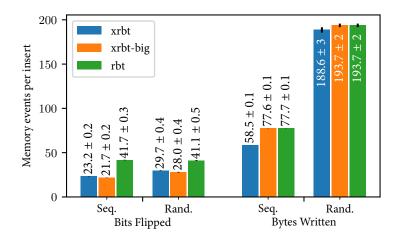

|     | A.4.5                                              | XOR Red-Black Trees            |  |

|     | A.4.6                                              | Cache Effects                  |  |

|     | A.4.7                                              | Manual Instrumentation         |  |

|     | A.4.8                                              | Stack Frames                   |  |

| A.5 | Perfor                                             | mance Analysis                 |  |

| A.6 | Discus                                             | sion                           |  |

| A.7 | Future Work                                        |                                |  |

| A.8 |                                                    | ısion                          |  |

|     |                                                    |                                |  |

Bibliography

115

## LIST OF FIGURES

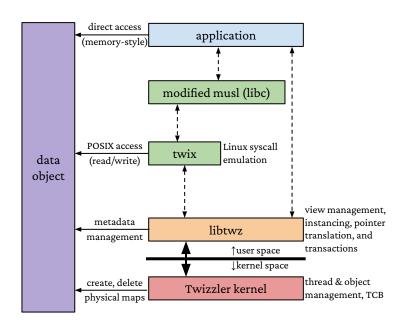

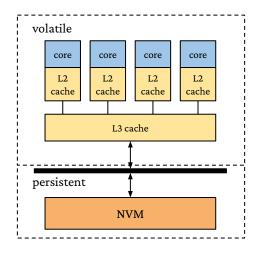

| Expected hardware system architecture                              | 10                                                              |

|--------------------------------------------------------------------|-----------------------------------------------------------------|

| The cycle of systems programming                                   | 14                                                              |

| Rendezvous of data and compute                                     | 19                                                              |

| Twizzler system overview                                           | 29                                                              |

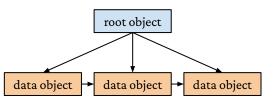

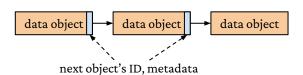

| Chaining objects                                                   | 36                                                              |

| Alternative object chaining                                        | 37                                                              |

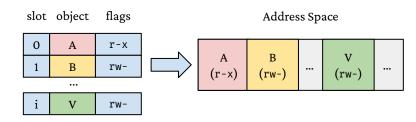

| Layout of a view object                                            | 39                                                              |

| Two-level translation scheme                                       | 41                                                              |

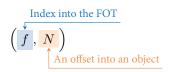

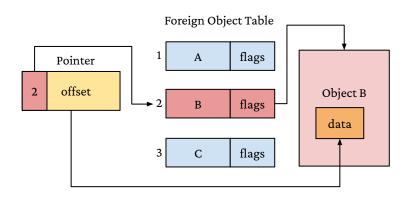

| FOT translation                                                    | 45                                                              |

| Invariant pointer Rust example                                     | 46                                                              |

| Invariant pointer C example                                        | 46                                                              |

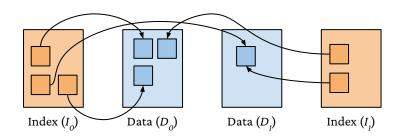

| Cross-object pointers                                              | 48                                                              |

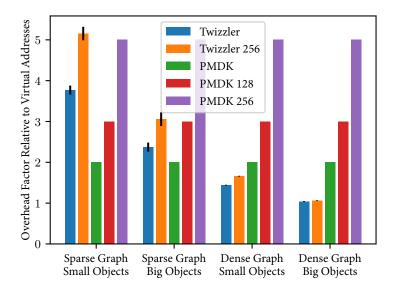

| FOT storage overhead                                               | 54                                                              |

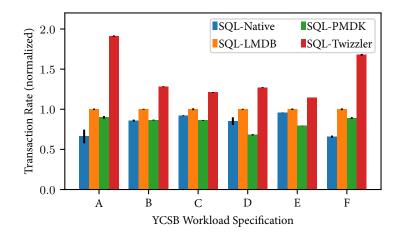

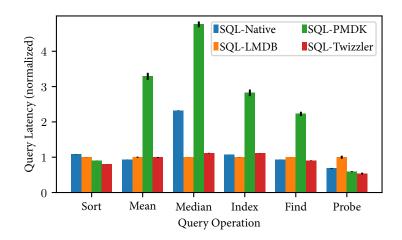

| YCSB throughput                                                    | 56                                                              |

| Query latency                                                      | 57                                                              |

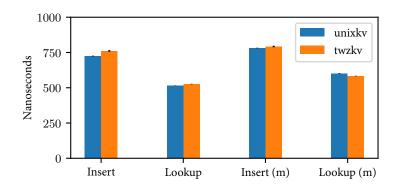

| Latency of KVS operations                                          | 58                                                              |

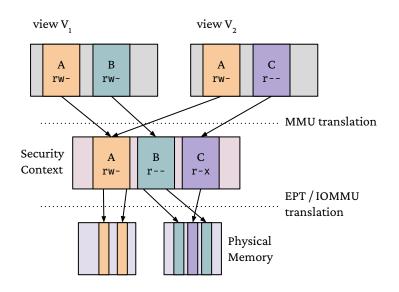

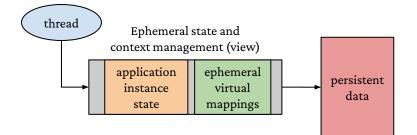

| View objects in Twizzler                                           | 62                                                              |

| Typical object layout                                              | 70                                                              |

| Volatile and persistent domains                                    | 72                                                              |

| Power use as a function of flips per second                        | 94                                                              |

| $Typical \ behavior \ vs. \ \texttt{iteration\_count} \ . \ . \ .$ | 102                                                             |

| Bit flips from malloc                                              | 103                                                             |

| XOR versus standard linked list characteristics                    | 104                                                             |

| XOR hash table characteristics $\ldots \ldots \ldots$              | 105                                                             |

| XOR red-black trees characteristics                                | 106                                                             |

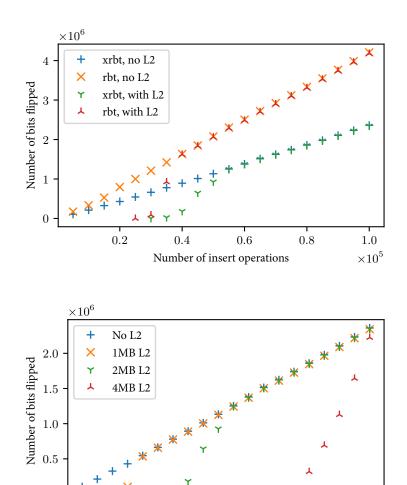

| XOR red-black tree bits flipped                                    | 107                                                             |

| XOR red-black tree bits flipped (varying cache)                    | 107                                                             |

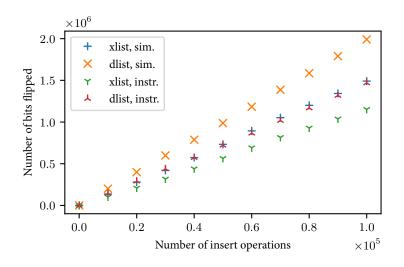

| Instrumentation vs. simulation for bit flips                       | 108                                                             |

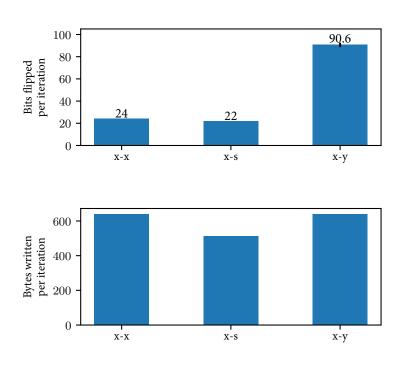

| Bits flipped by different stack frame layouts                      | 109                                                             |

| Bytes written by different stack frame layouts                     | 109                                                             |

| Performance of XOR hash table variants                             | 110                                                             |

| XOR red-black tree insert latency $\ldots \ldots$                  | 111                                                             |

| XOR red-black tree lookup latency                                  | 111                                                             |

|                                                                    | The cycle of systems programming Rendezvous of data and compute |

## LIST OF TABLES

| Table 6.1 | Twizzler primitives latency 55               |

|-----------|----------------------------------------------|

| Table 7.1 | Emulated syscall latency 68                  |

| Table A.1 | Cache parameters used in Gem5 102            |

| Table A.2 | XOR and standard linked list performance 110 |

## ACRONYMS

- NVM Non-volatile Memory

- KVS Key-Value Store

- DSM Distributed Shared Memory

## ABSTRACT

Operating systems are built and designed around two driving forces: the capabilities of hardware, and the demands of software. Yet traditional<sup>2</sup> operating systems and programming models have inertia, resulting in interfaces for new hardware following the designs of existing interfaces. As a result, programmers are limited in their ability to express the important parts of their programs due to the layers of compatibility and overhead thrust upon them, despite their persistent demands for higher throughput and lower latency. Operating system abstractions must evolve into the modern day. Merely relying on decades old abstractions and incremental change will relegate novel hardware of the last decade to a fate of access via interfaces designed for tape and spinning rust.

We stand before an opportunity to study how a confluence of trends may shift programming models away from a traditional, process-centric view point towards a *data-centric* one, in which *data* is the primary citizen of the system. This opportunity arises from trends in hardware that directly impact how we view the data access path and the responsibilities of the operating system and the kernel. The increasing speed of interconnect technologies draws computing nodes closer together in latency space, increasing the efficiency and useability of shared memory. Persistence, traditionally trapped low in the memory hierarchy, is leaking upward, as access speeds for persistent devices increase<sup>3</sup>. As a result, the overhead of the traditional kernel-driven data access path begins to dominate the cost of accessing persistent data. Finally, the increasing heterogeneity and disaggregation of compute and memory devices demands increased data and compute mobility, as software demands continued scalability, distribution, and raw speed.

This dissertation presents a new, data-centric operating system and programming model designed around the trends above. The data-centric approach reframes the goals of the operating system and enables us to re-imagine classic systems programming techniques into a model that *facilitates* data sharing instead of hindering it. For example, classical systems programming models and techniques tend to involve significant complexity and overhead in dealing with data persistence and sharing, such as expensive coarse-grained persistence operations, rigid RPC data models, and serialization. In contrast, our data-centric approach gets the kernel out of the way of the data access path, makes data mobile through invariant references whose meaning does not change depending on address space or machine<sup>4</sup>, and thus removes the need for serialization.

<sup>2</sup> Read: old.

<sup>3</sup> This includes new technologies like byte-addressible non-volatile memory DIMMs, but also improvements in SSD performance and interfaces.

<sup>4</sup> In contrast to virtual memory, whose references only have meaning inside a single address space.

#### X ACRONYMS

We will cover the motivation and hardware trends that lead to our design, define a design space based on those trends, and finally discuss Twizzler, a point in that design space that exemplifies the ideals we will discuss. We will evaluate Twizzler with case-studies that demonstrate system behavior, and efficacy and useability of our programming models, by building several new pieces of software for Twizzler. These, along with ported larger applications, will be used to demonstate the performance of Twizzler and its programming model, often showing performance increase just due to simplification of software layers. For Ellen, Steve, and Christina.

### PUBLICATIONS

- Daniel Bittman, Peter Alvaro, Darrell D. E. Long, and Ethan L. Miller. "A Tale of Two Abstractions: The Case for Object Space." In: *11th USENIX Workshop on Hot Topics in Storage and File Systems (HotStorage 19)*. Renton, WA: USENIX Association, July 2019. URL: https://www.usenix.org/conference/hotstorage19/presentation/bittman.

- [2] Daniel Bittman, Peter Alvaro, Darrell D. E. Long, and Ethan L. Miller. "Optimizing Systems for Byte-Addressable NVM by Reducing Bit Flipping." In: *Proceedings of the 17th USENIX Conference on File and Storage Technologies (FAST '19)*. Feb. 2019.

- [3] Daniel Bittman, Peter Alvaro, Darrell D. E. Long, and Ethan L. Miller. "The Flipside: A Bit Flip Saved is Power and Lifetime Earned." In: ;login: 44.2 (June 2019), pp. 27–31.

- [4] Daniel Bittman, Peter Alvaro, Pankaj Mehra, Darrell D. E. Long, and Ethan L. Miller. "Twizzler: A Data-Centric OS for Non-Volatile Memory." In: 2020 USENIX Annual Technical Conference (USENIX ATC 20). USENIX Association, July 2020, pp. 65–80.

ISBN: 978-1-939133-14-4. URL: https://www.usenix.org/conference/atc20/presentation/bittman.

- [5] Daniel Bittman, Peter Alvaro, Pankaj Mehra, Darrell D. E. Long, and Ethan L. Miller. "Twizzler: A Data-Centric OS for Non-Volatile Memory." In: ACM Transactions on Storage 17.2 (June 2021). ISSN: 1553-3077. DOI: 10.1145/3454129. URL: https://doi.org/10.1145/3454129.

- [6] Daniel Bittman, Peter Alvaro, and Ethan L. Miller. "A Persistent Problem: Managing Pointers in NVM." In: Proceedings of the 10th Workshop on Programming Languages and Operating Systems (PLOS '19). Oct. 2019, pp. 30–37.

- [7] Daniel Bittman, Matthew Bryson, Yuanjiang Ni, Arjun Govindjee, Isaak Cherdak, Pankaj Mehra, Darrell D. E. Long, and Ethan L. Miller. *Twizzler: An Operating System for Next-Generation Memory Hierarchies*. Tech. rep. UCSC-SSRC-17-01. University of California, Santa Cruz, Dec. 2017.

- [8] Daniel Bittman, Matthew Gray, Justin Raizes, Sinjoni Mukhopadhyay, Matt Bryson, Peter Alvaro, Darrell D. E. Long, and Ethan L. Miller. "Designing Data Structures to Minimize Bit Flips on NVM." In: Proceedings of the 7th IEEE Non-Volatile Memory Sys-

#### xiv Acronyms

tems and Applications Symposium (NVMSA 2018). Aug. 2018. URL: http://www.ssrc.ucsc.edu/bittman-nvmsal8.pdf.

[9] Daniel Bittman, Robert Soule, Ethan L. Miller, Vishal Shrivastav, Pankaj Mehra, Matthew Boisvert, Avi Silberschatz, and Peter Alvaro. "Don't Let RPCs Constrain Your API." In: *The Twentieth* ACM Workshop on Hot Topics in Networks (HotNets '21). Nov. 2021.

### ACKNOWLEDGMENTS

None of this work could have been completed without tremendous help, guidance, support, and love. I'd like to say a few words about all the people who came together to realize this thesis.

My partner, Emily Zierdt Smith, has been my biggest supporter throughout my studies, and has stood by me through good times and bad during my PhD. She has given me feedback, helped me formulate and make sense of my thoughts and myself, and, with great patience and love, has helped me along the way through the marathon that is graduate school. Perhaps one day I can repay her kindness and patience for these graduate school years, but that may take a lifetime.

My PhD would have been over before it began if not for the guidance of the members comprising my dissertation committee, who, in no small way, provided me the support and the environment I needed to succeed. In no particular order, I want to profusely thank:

- Peter Alvaro, whose blue-sky insights have shaped this work and story like no other.

- Ethan Miller, with his concrete and meticulous approach to systems engineering.

- Darrell Long, whose kindness is matched equally well with invaluable critical feedback.

- Pankaj Mehra, whose propensity to probe at the difficult questions of research always leads to better understanding.

The above list is in no way meant to imply that these qualities are completely unique to each person; on the contrary, I look up to these people precisely because they all share these vital qualities in a mentor. They have all provided me guidance and training for analyzing problems, building mental models, probing those models, designing experiments, running and managing them, collecting and processing data, turning that into new knowledge, and of course, communicating that knowledge. And, perhaps most important of all, zooming out and looking at the big picture. I can only hope to emulate their brilliance going forward.

I will never forget the unending support from my lab mates, in no particular order, Dev Purandare, Peter Wilcox, Michael Usher, Achilles Benetopoulos, Esteban Ramos, Matt Bryson, Staunton Sample, Yan Li, Lincoln Thurlow, Oceane Bel, Ken Chang, Sinjoni Mukhopadhyay, Jim Hughes, James Byron, and Yuanjiang Ni, among others. My work would not have come together if not for whiteboarding sessions, feedback, and discussions with these fine folks. I want to explicitly thank DJ Capelis, who mentored me during the last few years of undergrad and helped induct me into a graduate lab and give me a taste for research from which I never recovered. I will miss you all, but don't think that you'll never see me again.

I'd additionally like to thank Robert Soulé, Avi Silberschatz, Shel Finkelstein, Andrew Quinn, Ike Nassi, Heiner Litz, Pat Heland, Bruce Lindsay, and Ahmed Amer for their feedback and discussions. Having the ear of these brilliant people, but more importantly listening to their insights, has been invaluable.

Unfortunately, my time in graduate school will forever be tied to the COVID-19 pandemic. I am forever grateful to my labmates for working hard to maintain morale. I will cherish our remote tea times. My heart goes out to all graduate students who suffered in academia during these last few years.

Finally, all of my friends and family who stuck with me and supported me over the years. You are all amazing, and I love each and every one of you. My parents and sister never ceased in their unending support, and I cannot thank them enough. This dissertation is dedicated to them, from the bottom of my heart.

Thank you, all.  $\heartsuit$

Daniel Bittman

"I wish it need not have happened in my time," said Frodo. "So do I," said Gandalf, "and so do all who live to see such times. But that is not for them to decide. All we have to decide is what to do with the time that is given us."

> *—The Lord of the Rings*, J.R.R. Tolkien

### FOREWORD

This dissertation presents a narrative. That narrative is, at time of writing, the best understanding of the work that I have. Any researcher knows that one doesn't start a research expedition with a fully formed understanding of a narrative in-mind; instead, that narrative grows and changes dramatically with each success, but more importantly with each failure. And while I'd like the narrative—the *story*—of the work herein to contain not just the sapling that is the product of my time at UCSC, but also the dead branches that I've pruned along the way, such story telling would distract from the scientific communication of this work. But I'd like to expose a sample of that more accurate, but no less "true", story here.

One might well question the logic behind prefacing this dissertation with a refutation of its presented narrative. However, I think it's important to consider what effect a work may have upon a reader. In particular, if even one student reads these chapters and comes away with a belief that the scientific process (and, more specifically, the Ph.D. process) is linear and *not* an experience of one feeling their way through a dark labyrinth, then I will have been negligent in my duty to help future students and avoid harming them.

Twizzler started as a combination of two things: my love for hacking kernels, and an idea for a new OS focused on the exciting new technology of byte-addressable non-volatile memory (NVM). It has since grown well beyond that limited scope, but at the time, that limitation allowed me to get started. We hadn't yet figured out the "big picture" words to use to describe what we were trying to do, instead we presented the work as a straight-forward design to improve performance for applications on NVM. It seemed like the perfect time, with Intel releasing 3D-Xpoint memory, and the interest in NVM exploding. All I had to do was build an operating system to manifest the designs we'd been whiteboarding.

I started by prototyping the ideas inside FreeBSD, modifying the kernel to act like we wanted it to. This was largely a dead end, since we rapidly ran into walls trying to force a UNIX kernel to be something it wasn't. The FreeBSD prototype was superceded with a custom kernel and grew into the main Twizzler operating system that is presented herein. It needed to be reworked and redesinged several times, each time leading to me pulling long nights programming and writing. But, in the end, the system worked, despite us not yet having the right words to describe it.

Since I mentioned failure earlier, let's talk about publications. It took us *years* to get Twizzler published in a conference. Along the way we had two workshop publications, but the rejection notifications from conferences

BASHIR: Out of all the stories you told me—which ones were true, and which ones weren't? GARAK: My dear doctor! They're all true. BASHIR: Even the lies? GARAK: Especially the lies.

-Star Trek: Deep Space Nine

Audiences know what to expect, and that is all that they are prepared to believe in.

-Rosencrantz and Guildenstern Are Dead, Tom Stoppard

#### All this happened, more or less.

-Slaughterhouse-Five, Kurt Vonnegut were, shall we say, starting to get to me. Fortunately, I had supportive professors who showed me their "co-CVs", containing lists of rejected publications. I started keeping one as well. This is all to say—if you're a student, and you are struggling to publish: we have all been there<sup>5</sup>, and (despite how some program committees behave) we are rooting for you. Maybe one day our academic publishing system will function well.

I've also had blessings in disguise. As I said earlier, the initial writings on Twizzler framed the work nearly exclusively around NVM and performance ("getting the kernel out of the way"). Looming on the horizon, however, was the growing certainty that NVM (or, at least, 3D-Xpoint) would *not* soon deliver on its promises. Looking back, we got lucky. We were forced to rethink the narrative, to look at the forest instead of the trees, and I think the work is much stronger as a result. We were able to generalize. In fact, one of the benefits to the design presented in Chapter 6 is that, while we built it for NVM at the start, it is actually quite generalizable to larger contexts, and so much of the technical design work for Twizzler wasn't lost during this rethinking of the narrative.

The research process is labyrinthian, and never ending. The snapshot of work presented here is distilled into a story that is, in my opinion, straight-forward and compelling. But the road to get here was long, filled with pot holes, dead ends, and complete reimaginings. I hope you enjoy reading it as much as I have enjoyed making this crazy idea a reality.

۰

$\heartsuit \heartsuit \heartsuit$

Daniel Bittman

<sup>5</sup> Anyone who claims to know, in full, what they are doing, is a *liar*.

Part I

## PRELUDE

*It's the best possible time to be alive, when almost everything you thought you knew is wrong.*

—Valentine, Arcadia, Tom Stoppard

## INTRODUCTION

Let's design and build a new operating system.

#### THE MOTIVATION

The confluence of several hardware trends—persistent memory moving up the memory hierarchy, faster interconnect technologies, and increasing heterogeneity of compute and memory—demands a fundamental shift in how we view applications' relationships with hardware and data. As persistence gets closer to compute in latency space, the line separating the traditional two-tier memory hierarchy of fast, volatile memory and slow, persistent storage begins to blur. Meanwhile, interconnect technologies are improving, causing separate computing nodes to be drawn closer to each other in latency space, allowing them to more efficiently share memory. Computing resources are spreading out, as we race to place computing units in devices and near memory, and as we start seeing different kinds of physical memory on the bus, the traditional host-centric and process-centric models of programming give way to models that better express the increasing demands for concurrency and parallelism between devices and computers.

Software both drives some of these trends, as it demands increasing throughput and lower latency when processing data, but is also affected by the trends, or more specifically, often limited in expressivity to what *abstractions* are presented to software by the operating system<sup>6</sup>. The primary goal of a program is to access and operate on data. Any additional required work that an application must perform to enable that goal is overhead, both in terms of performance (latency or throughput) but also *complexity*. Applications must routinely pay significant overhead costs that ultimately source from the abstractions and programming model enabled by the operating system, which is in turn sourced from a model of hardware decades old. Traditional operating system abstractions and interfaces do not adequately reflect current hardware, the direction hardware is heading, nor the demands of software upon those interfaces.

#### THE OPPORTUNITY

We have an opportunity to examine hardware trends and evolve operating system design to make the best possible use of new technologies and

# 1

"Sometimes I find the best way of getting from one place to another is simply to erase everything and begin again."

> *—The Phantom Tollbooth*, Norton Juster

<sup>6</sup> OS abstractions, a favorite punching bag!

Two roads diverged in a wood, and I— I took the one less traveled by, And that has made all the difference.

—Robert Frost

#### 4 INTRODUCTION

trends. Mere incremental change will not enable the dramatic improvements in performance and complexity heralded by these trends, just as SSDs did not reach their full potential until they transcended the disk paradigm<sup>7</sup>. Instead, we will discuss and examine a "clean-slate" approach to operating system design that avoids trying to mold new hardware into some backwards-compatible existing box<sup>8</sup>. Such an approach will necessitate examining past research and reconsidering previously impractical ideas<sup>9</sup> while extending those ideas for modern software, hardware, and languages. Simultaneously, we must design new abstractions and interfaces that expose a programming model that allows applications to center around the data they are accessing while not requiring them to twist into knots trying to best utilize modern hardware.

Our focus will be on a *data-centric* approach, in which *data* is the primary citizen instead of the process. As we will see, this framing around data forces us to reconsider and reimagine classic systems programming tropes like explicit, coarse-grained persistence barriers, call-by-smallvalue RPC, shared memory, serialization, and in-memory data structures that cannot escape the bounds of a single process<sup>10</sup>. We will define a design space for data-centric operating systems that centers around in-memory data in a global address space that can be shared across both space and time, whose lifetime is disconnected from ephemera like processes, nodes, and virtual address spaces, and which can be operated on, persisted, and shared without the overhead of operating system involvement in the data access path<sup>11</sup>. In a world where in-memory data can last forever and move across processes and nodes, the context required to manipulate that data is best coupled with the *data* rather than ephemeral constructs. Data has always been the focus of programming; it's time our operating system abstractions adequately capture this simple fact.

#### THE IMPLEMENTATION

The principal hypothesis of this dissertation is that the data-centric model for designing operating system abstractions is not only viable, but demanded both by software and hardware trends. Examining this hypothesis will require answering a number of questions about the design space, the practicality of any implementation of our ideas, and empirical measurements of that implementation. To study data-centric operating system design, we have built *Twizzler*, an operating system that embodies the ideas presented herein.

Twizzler consists of a standalone kernel built from scratch, a set of userspace libraries for programming memory, and a set of applications we wrote and ported for evaluation. It provides a rich environment for programming in-memory data structures that can be shared and persisted by presenting data access as memory access within a (very) large global <sup>7</sup> Arguably, they still haven't. SSDs were, for a long time, treated as "fast disks", to the detriment of our storage stacks.

<sup>8</sup> Imagine if we tried to access, say, persistent RAM with interfaces designed for magnetic tape! *Stares straight into the camera*.

<sup>9</sup> Knowledge derives from experience of the world, but what if that world were to change?

<sup>10</sup> See Chapter 3.

<sup>11</sup> See Chapter 4.

address space in which references to *any other piece of data* are efficiently encoded. Traditional operating system abstractions reflect the hardware they are designed for, and Twizzler is no different. Twizzler's abstractions for data access center around two core concepts: **remove the kernel from the data path**, and **enable the construction of in-memory data that is free from ephemeral context**. We will see how these core concepts manifest, both in how they enable new ways of building applications and in how they improve performance when accessing data.

#### THE CLAIMS

This dissertation, in addition to investigating the aforementioned principal hypothesis, makes the following claims:

- Retrofitting existing interfaces is insufficient. Instead, the correct approach to reimagining programming in a world of changing memories is to rebuild the operating system from the ground up. Similarly, backwards compatibility, while important, is not the primary goal of a reimagined system. Applications that want to adapt to new hardware trends should get first-class support.

- A global address space of all data is a viable design for long-lived, in-memory data structures, and access to that address space can be done efficiently with little kernel involvement<sup>12</sup>.

- 3. The implementation of references within the global address space matters beyond simple performance tradeoffs. We can encode references within the address space to not only be *invariant—i.e.* not based on any local context—but we can also encode them efficiently, despite the address space being large, with less space overhead than alternative approaches<sup>13</sup>.

We will examine these claims in more detail throughout the following chapters, keeping in mind the goal—that by providing in-memory data structures that don't require kernel intervention in the data access path we can center programming around data instead of actors. Showing a viable approach to low-coordination global data naming and accessing is the primary piece of the puzzle. But after we place this puzzle piece, there is still much work to do—the operating system must provide basic services, convenience libraries, interfaces for ensuring safety in failure-atomicity and type correctness for persistent data, and (last but *certainly* not least) security<sup>14</sup>. These aspects are no less important than the enumerated claims, however we will approach them in such a way that ties them back to be fundamentally derived from the core concepts of Twizzler.

<sup>12</sup> See Chapter 5.

<sup>13</sup> See Chapter 6.

<sup>14</sup> See Chapters 7 and 8.

#### 6 INTRODUCTION

#### THE SIGNPOSTING

**Chapter 2** discusses, in detail, the hardware trends we are considering and the implications they hold, followed by a discussion of how those trends will inform our operating system design work.

**Chapter 3** covers the software demands of hardware and interfaces, primarily focused on the overheads that software has to deal with to get around "the context problem". We will cover serialization<sup>15</sup> for persistence and distribution as well as patterns of RPC.

**Chapter 4** combines the insights from the previous two chapters and discusses data-centric operating system design, introduces Twizzler, and provides an overview of relevant operating system, persistent memory, and systems research.

Following Chapter 4, we begin to focus more specifically on the design and implementation choices we made for Twizzler, studying them in case studies, performance analysis, and modeling. **Chapter 5** covers the design of the global address space in Twizzler, the model of data objects Twizzler uses, and models the collision possibility of object IDs within the space. Finally, it discusses how the global address space is realized and accessed on existing hardware.

**Chapter 6** discusses how we encode references within the global address space, introduces the *foreign object table*, our solution to naming data in an invariant fashion, and performs case-studies on using invariant references to build real data structures that serve as a backend to a ported version of SQLite. These software are then evaluated for performance and compared to other solutions to persistent memory programming.

**Chapter** 7 enumerates several core aspects of Twizzler as an operating system, such as object services, program instancing, threading, security, and UNIX compatibility.

**Chapter 8** goes over higher level programming concepts, such as failureatomicity, type safety, memory safety, crash consistency, and new patterns enabled by Twizzler's object and invariant references model.

**Chapter 9** concludes with a look back on the presented work and a look to the future for operating systems, Twizzler, and data-centric designs.

Twizzler is open-source and can be found at twizzler.io<sup>16</sup>.

"Being lost is not a matter of knowing where you are. It's a matter of knowing where you aren't."

> — The Phantom Tollbooth, Norton Juster

<sup>15</sup> "Boo"ing sounds.

#### FAR OUT MEMORY HIERARCHIES

**SYNOPSIS** The world is changing around us! This chapter introduces the hardware trends that we observe and discusses some of the details behind our expectations of how these trends will pan out. We will discuss persistence, including both SSDs and NVM, along with memory disaggregation, interconnect technologies, and device controller complexity.

Operating systems provide abstractions for data access that reflect the hardware for which they are designed. For example, our current I/O interfaces reflect a structure that takes as axiom the separation between volatile and persistent data domains. Any assumptions we make about hardware, however, may become less accurate over time, resulting in an increasing impedance mismatch between the interfaces provided and the underlying hardware.

It therefore pays to examine the trends in hardware<sup>17</sup> and reexamine how we expose that hardware to applications. The work presented herein starts with the assumption that hardware trends are, at minimum, worth examining to see how we may wish to update our interfaces. We argue further that the trends and opportunities we are presented with demand a full scale revolution in how programming models are designed, and in the design of operating systems that wish to support new models. Let's first explore some hardware trends, and then, in the next chapter, put those trends in the context of the software that we wish to better support.

#### 2.1 MEMORY AND COMPUTE

Memory and storage are getting closer *and* further away<sup>18</sup>. Closeness of memory to CPU in latency space has long been a vital part of ensuring speedy computation. However, in the constant battle between latency and throughput (and complexity and density), latency often loses, and the latencies of DRAM have not seen dramatic reductions for some time. Meanwhile, access to *persistent* memory is getting faster in latency *and* throughput. Not only are SSDs improving, but so too are the protocols they use and the link speeds between them and main memory [77, 129].

Recently, we have also seen commercially available byte-addressable Non-volatile Memory (NVM) in a DIMM form-factor. This technology, Intel Optane<sup>19</sup> (using 3D-Xpoint technology), provides a persistent memory with low latency—only  $1.5-8\times$  the latency of DRAM in most

## 2

"I never am really satisfied that I understand anything; because, understand it well as I may, my comprehension can only be an infinitesimal fraction of all I want to understand about the many connections and relations which occur to me, how the matter in question was first thought of or arrived at..."

-Ada Lovelace

One of the most basic goals is to build up some abstractions in order to make the system convenient and easy to use. Abstractions are fundamental to everything we do in computer science. Abstraction makes it possible to write a large program by dividing it into small and understandable pieces [...] Abstraction is so fundamental that sometimes we forget its importance.

> —Operating Systems: Three Easy Pieces [3]

<sup>17</sup> And software, as we will see in the next chapter.

<sup>18</sup> Bear with me, now!

<sup>19</sup> We will discuss the outcome of Intel's "attempt" to market this technology later.

cases [61]—that is accessible from the CPU via normal load/store instructions. Direct, low latency access to NVM opens the door to building systems around persistent data structures and avoiding serialization<sup>20</sup>.

We can view the emergence of NVM as an extreme example of the general trend of persistence getting closer to compute. As a result, the relative cost of indirection and kernel involvement in the data path is increasing. While before the cost of a system call was significantly less than that of the actual device activity, now we are seeing the cost of device access shrinking to a similar magnitude of the cost of a system call, or in the case of NVM, even less.

#### 2.1.1 Distribution

However, to stop here would be a mistake. Another significant trend is *disaggregation*, in which memory is placed across machines and programs are written expecting various levels of access to this distributed memory. This is, admittedly, as much about software as it is about hardware, however there are underlying hardware mechanisms that are driving the push toward decoupling memory and compute. On a network level, renewed interest in Distributed Shared Memory (DSM) is sourced from a combination of several factors:

- Network speeds are continuing to increase. With technologies like 100 Gigabit NICs and 10 Tb/s switches, previous limitations on distributed memory that arise from network performance reduce or go away entirely.

- 2. Network hardware complexity is increasing. Not only can those switches sustain 10 Tb/s of throughput, but they can also be programmable, allowing the network to have much more participation in protocols. Furthermore, we are seeing protocols like RDMA enabling remote memory access via the network.

It isn't just traditional networking in which memory semantics are leaking out past a single traditional node. Interconnect technologies like CXL have the potential to upend the traditional view of "CPU attached to memory with peripheral devices" as the fundamental concept of a node. These trends mirror the persistence trends above—things that were traditionally far away (other nodes' memories) are getting closer in a logical space, and things that were close (local DRAM and storage) can be more efficiently shared.

Finally, improved fabrication techniques and shrinking feature sizes means hardware controllers are increasing in complexity, offering more autonomy from the CPU, off-CPU processing capabilities, and better parallelism. Hardware interfaces reflect the controller complexity expected <sup>20</sup> Indeed, this is what we will do.

of devices; for example, AHCI controllers improved request queuing over ATA, and DMA allows hardware to copy data directly to and from memory independently from the CPU. NVMe expands the responsibility of controllers again, adding deeper and parallel command queues, requiring devices to multiplex requests themselves and allowing them to exploit the parallelism of access available in SSDs. We expect these trends to continue, resulting in more programmable hardware devices that are able to act on shared, global memory with more autonomy.

#### 2.1.2 Memory Density

Another point to make is one of increasing memory sizes, largely stemming from increased density of memory technology. Not only can we see this in DRAM, with well-known systems taking advantage of increased DRAM sizes [94], one of the major selling points of Intel's Optane NVM was a significant increased density and lower cost per byte. Having larger memories means a few things:

- Some nodes may have wasted memory as workloads come and go. This ties in with the above points about disaggregated memory sharing unused memory is more cost effective, since unused RAM is wasted RAM.

- 2. Memory can have an induced-demand effect. Similar to how building additional lanes on highways often just increases traffic [17], making more memory available can cause additional memory traffic since working sets can be larger.

- 3. In-memory sharing can increase. With significantly larger memories, applications can take advantage by not writing intermediate results to storage, and instead can write to shared memory.

#### 2.1.3 The Heterogeneity of Memory

The advent of NVM in a DIMM form factor has given us further motivation to consider the effects of a heterogeneous memory environment. When all memory is a single "kind" (*e.g.* DRAM), it matters little from where in the physical address space memory is allocated, since devices (including the CPU) can only access one kind of memory between them<sup>21</sup>. However, if our physical memory is comprised of multiple kinds of memory, we must be more careful with our allocation. Programs may request allocations of memory for their data based on different policies of what kind of memory they want—volatile versus persistent, high-bandwidth versus DRAM, to name a few.

<sup>21</sup> Yes, older devices are limited in address space, but this is not important, and I do not wish to get stuck in the past.

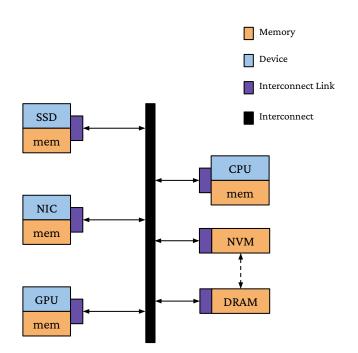

#### FIGURE 2.1

Our expected system architecture. Solid black lines show data paths. Dashed lines and boxes show potential dedicated paths.

But it's not just allocation policy that is affected. Having different kinds of memory means that large-scale movement of data between regions of physical memory is now semantically meaningful and may be triggered as a result of policy, evictions, *etc.* Interacting devices, therefore, must coordinate on a shared mapping of logical data to physical data, as the physical data might move between kinds of memory. One could easily argue that this heterogeneity is not actually new—with NUMA, we see many of the same problems. I agree! However, the correct solution is to design around a fundamentally heterogeneous memory system and build the concepts of data movement across physical memory into the core abstractions. Such a model is not only useful for the advent of NVM on the memory bus, but it also covers future additions of different kinds of memory as well as subsuming the NUMA model.

#### 2.2 SOME KIND OF MODEL

These changes are coupled with a shift in focus for how data moves throughout the system. Traditionally, data is considered to move into main memory for computation by the CPU, followed by storage to persistent memory (through a disk or SSD controller) or moved out onto the network (through a network controller). Figure 2.1 shows a different model, where data is able to more fluidly move through the system, or even needs less movement. With more complex controllers and off-CPU processing, we expect non-traditional data paths to become more common. Say, for example, a packet arrives at the NIC containing compressed data for GPU processing. A traditional system would move the compressed data into main memory, decompress it using the CPU, and move it into GPU memory for processing. Instead, we could see a dedicated compression chip in the NIC whose job it is to decompress incoming data. That data could then be moved directly between the NIC's buffers and the GPU memory, without involving the CPU and main memory at all. This both reduces copies and frees these resources for other uses.

Note the rather generic model in Figure 2.1. We are intentionally not ascribing specific properties to the components protrayed within. Attemping to build generic system abstractions atop an abstracted model while not losing too much in the abstraction is a fundamental essence of operating system design. Here, we are trying to capture the basic ideas of the trends we discussed—individual, higher powered devices, accessing shared memory pools and possibly each others' memory pools, with possible NVM and fast interconnects that allow addressing control and isolation<sup>22</sup>. Concretely, we can see this model mapping well to, for example, CXL, and even current PCIe systems<sup>23</sup>. As the trends we observe continue, the inherent concurrency enabled by allowing devices to operate more independently with more ability to share memory without waiting for permission from the CPU and the reduced lengths of code paths in processing data points strongly to a model like the one we describe here.

#### 2.3 SO, WHAT DOES THIS ALL MEAN?

The trends above imply several basic requirements for a set of operating system interfaces:

REMOVE THE KERNEL FROM THE DATA ACCESS PATH The cost of system calls is too large relative to device access to justify their use in the data path. We must provide lightweight, direct, memory-style access for programs to operate on data.

ASSUME DATA LIFETIME IS DISCONNECTED FROM EPHEMERA Memory can now be pooled in units outside the purview of the CPU. This can happen either in time—data can be persisted, where the CPU loses control over that data when power is cycled—or in space—where data can traverse a network, or be accessed by multiple devices on an interconnect. <sup>22</sup> Cache coherence is an issue that we are not explicitly designing for or against. It remains to be seen how cache coherence between these devices will play out. Nonetheless, the issues of coherence and failure-atomicity are not lost on us, and we will discuss them in Chapter 8.

<sup>23</sup> If we squint our eyes and have perhaps undue faith in the IOMMU. While these forms of temporal and spacial sharing have always existed, they have either been relegated to "experts" in cordoned off low-level areas of the system (drivers and DMA) or have been explicitly designed around by, for example, building OS abstractions around an assumed bifurcation of data into "volatile" and "persistent" domains, and asking programmers to explicitly move data between them<sup>24</sup>.

However, when the previously outcast domains of persistence and network become closer to compute as we saw above, either via faster access or pushing compute power further out, we must **design for in-memory data structures**. Long-lived data structures can directly reference persistent data, so references must have the same lifetime as the data they point to. Virtual memory mappings are, by contrast, ephemeral, and so cannot effectively name persistent or distributed data. But perhaps more importantly, in-memory data structures are *what we compute on*, and it's *computation* that matters most. If we can reduce or even remove extraneous processing paths that waste time, we should take that opportunity.

TOWARDS A DATA-CENTRIC OPERATING SYSTEM We call an operating system that meets both of the above requirements *data-centric*, as opposed to current OSes, which are *process-centric*. Facilitating operations by applications on in-memory data structures is the primary function of a data-centric OS, which tries to avoid interposing on such operations, preferring instead to intervene only when necessary to ensure properties such as security and isolation. To meet both of these requirements a data-centric OS must provide effective abstractions for identifying data independent of data location, constructing persistent and distributed data relationships that do not depend on ephemeral context, and facilitating sharing and protection.

WHY NOW? It is natural at this point to wonder, "why now? The memory hierarchy has *always* been changing." This is true, but there are a few unique elements to the recent changes we are seeing. First, the placement of NVM directly on the memory bus is a fundamental dramatic shift in how we view persistence and opens the door to *true* single-level stores. Second, the increasing distribution of both memory and CPU requires that we rethink how computation is delegated throughout the system and how those separate memories and devices can organize, access, and reference data. But, more fundamentally, this thesis argues that our datacentric model was *always* the correct model. We just have an opportunity to realize it, and modern hardware has the ability to make it efficient and scalable. The memory hierarchy has always been changing, but our interfaces have not kept pace. It is time for a revolution, designed for new hardware and, as we'll see in the next chapter, informed by software. <sup>24</sup> We will explore this more fully in the next chapter.

#### THE DEMANDS OF SOFT WARE

**SYNOPSIS** This chapter will focus on software, the needs of software we must address, and the perspective of systems programming, putting the hardware trends we spoke of last chapter into context. We will discuss the problem of ephemeral context and discuss how persistence and RPC have shared characteristics and concerns.

At their core, applications perform computation on in-memory data. Yet much application complexity is tied up in the infrastructure surrounding that computation, for example, in managing persistent state and in performing serialization. Additional work done by the program (or by the operating system on behalf of the program) that is merely in service of setting up the computation and not the computation itself is considered *overhead*. Our goal is to reduce that overhead in two ways: improving performance and reducing complexity. To do this, we need to understand where overhead comes from, which elements are fundamental, and which are not.

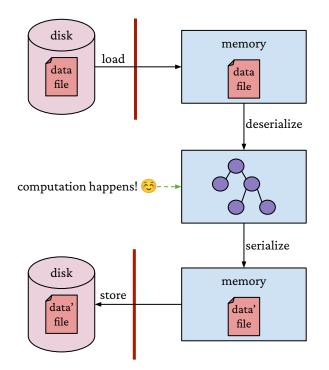

## 3.1 THE OLD WAYS AND "SYSTEMS PROGRAMMING"

Current operating system interfaces are a poor fit for the trends and hardware requirements we discussed last chapter. File read and write interfaces, originally designed for sequential media and later expanded for block-based media, require significant kernel involvement and often serialization, violating both the requirement to reduce kernel involvement, and the need to reduce the length of code paths around accessing data. Figure 3.1 shows a fairly common data path for an application that operates on (and perhaps mutates) some persistent data. First the data is loaded explicitly into memory, either in a streaming fashion or as a whole file, followed by the application manually deserializing it into an in-memory form. Once this is done, the program may commence its actual purpose—to perform computation—after which the results are serialized and placed back onto disk with an explicit store operation.

Let's consider the case from Chapter 2 of faster, closer persistence. In the past, the overhead in manually loading and unloading data and in transforming it to and from an on-disk form was acceptable, since the cost to access the disk was high, and those explicit load and store disk operations were going to be issued anyway. But when these operations

## 3

"So many things are possible as long as you don't know they're impossible."

> *—The Phantom Tollbooth*, Norton Juster

One goal in designing and implementing an operating system is to provide high performance; another way to say this is our goal is to minimize the overheads of the OS. Virtualization and making the system easy to use are well worth it, but not at any cost.

> —Operating Systems: Three Easy Pieces [3]

#### FIGURE 3.1

The "standard cycle" of systems programming. We start with some persisted data, explicitly load it from disk into memory, deserialize it, compute on it, reserialize it, and explicitly store it back to disk. Note that the vast majority of this diagram depicts stuff other than the actual computation. The thick red lines depict persistence boundaries, across which data exists in different contexts and assumed lifetimes.

overshadow device access time, the overhead quickly becomes unacceptable. As devices become faster and as applications process more and more data, we find that more and more of our processing time is spent here. Applications can spend as much as 70% of the processing time [30] deserializing and loading data into main memory at request time. Reducing this overhead would save both in program time but also in *programmer* time. Simplifying applications by removing serialization helps programmers by removing the need to maintain multiple data formats and the transformation code to move data between those formats.

#### 3.1.1 The Context Problem

If we look closely, the cycle in Figure 3.1 can represent more than just processing files. It works equally well for receiving data from a network and sending back a response (microservices and servers in general), or for applications in a traditional pipeline, *etc*<sup>25</sup>. But why do we often spend so much time and effort with serialization and explicit I/O? Because the POSIX abstractions fundamentally bifurcate our programming model into two separate *contexts*:

1. Local Context contains data that is limited to a single domain, for example in-memory data accessed via virtual addresses by a single

<sup>25</sup> Those who sit high atop their UNIX throne claim that text is a universal communication language. Yet anyone who has actually had the misfortune of parsing the output of even a moderatly complex UNIX tool can realize that systems programming here involves just as much serialization and processing work as anywhere else—or else involves doing computation directly on C strings, a fate I would not wish upon my worst enemy. process, or the domain of file descriptors. Data in a local context is typically operated on "directly" since it's usually in memory. Most importantly, though, the data isn't *shared* with other domains, and it is ephemeral—its lifetime is tied to the context it is in.

2. Global Context contains data that is shared across all the domains. Typically this covers data stored on disk or other stable storage. Data in a global context is usually stored in some serialized format and can be accessed by multiple domains simultaneously. The lifetime of data herein is, in the limit, infinite<sup>26</sup>.

These separate contexts give rise to the need to transform data between them and to be explicit about marshalling data across the boundary. The primary reason for the need for transformation has to do with *data references* and *naming data*. For example, when applications operate on in-memory data, references take the form of virtual addresses—pointers refer to specific locations within the virtual address space. The virtual address space is ephemeral—it's tied to a specific process. But *persistent* data is *not* ephemeral! By definition it is accessed by multiple processes, either over time (different invocations of the same process), or across space (shared between multiple processes), or both. In either of these cases, virtual addresses cannot be used, since those addresses may not agree across different contexts. So when sharing memory, any references to local context data must be transformed into something that can be interpreted within the global context.

More generally, we often lock data access behind context that is tied to a shorter-lifetime actor, leading to unnecessary indirections and extraneous work that the program must perform. This is illustrated in how data relationships are typically handled, either:

- Explicit, context-sensitive. As we saw with virtual address pointers, references between data are encoded explicitly but rely on context provided by the ephemeral process abstraction. These references cannot be reliably shared between applications and across nodes which do not have the context necessary to interpret them.

- 2. **Implicit.** Many data relationships are implicit in applications. Although there is a relationship between the UNIX files /etc/shadow and /etc/passwd, it is not explicit. This limits interoperability between programs, prevents relationship discovery, and results in a brittle environment if these files are moved or replaced.

- 3. **Explicit, via mediators.** Relationships can be encoded explicitly without ephemera if we use a global name resolution service. For example, an HTML file can refer to a style sheet by name. However, this presupposes the existence (and availability) of a global

<sup>26</sup> Even in the global context, we traditionally separate local storage and network storage. That separation can be eroded depending on the programming model, however, as we will discuss later. mediator and restricts programs from agreeing on the identity of data behind a reference without complex inter-networking and expensive global coordination.

In our view, the complexity of these mechanisms is a symptom of a more fundamental problem: access to long-lived data is unnecessarily mediated via ephemeral actors. We advocate a violent break from this actor-centric model of data access, in favor of a model that elevates *data* as the systems' first-class citizen. Doing so will require *explicit context-free* references via globally unique identifiers (GUIDs) that name data objects. These references are independent of context (*e.g.* process) that operates on them, and require that all context necessary to interpret references be stored within the data itself. Of course, we still need some understanding of context-sensitive relationships, for example late-binding of names. We do this via a "two-level" naming system in which GUIDs are *authoritative* names to which we can bind additional names for purposes like local references, changing data identification, and discovery<sup>27</sup>.

Viewing the past through the lens of the present, it was *always* a mistake to entangle the context required to access and manipulate data with ephemeral actors. However, in the days of slow networks, spinning disks and small memories, it was possible to hide these complexities and inefficiencies. For one thing, disk-based I/O led to a model of sharing in which long-lived data and computable data were stored in different *kinds* of memory, in different formats (due to serialization), with different reference formats (e.g., file names vs. virtual memory pointers). The filesystem was a natural location to place the various hacks that were required to paper over the reality that interacting with long-lived data required figuring out how to name the short-lived processes that were the primary citizens of the operating system.

Needless to say, a disaggregated system model—one in which a particular data reference may ultimately point to data on a different node from the one observing the reference—exacerbates all of these problems! Two different nodes that observe the same data reference should agree on what data is being referred to, and by the same token, an individual node observing two different data references should be able to determine if they point to the same data. This asks the question of *how* to encode these explicit context-free data references while remaining efficient and avoiding global coordination<sup>28</sup>.

#### 3.2 RETROFITTING POSIX?

While I am arguing strongly that a clean-break reimagining is needed, it is worth considering what an incremental approach might look like. For example, the problem of direct access might be solved to some extent <sup>27</sup> We will discuss these in more detail in Chapter 6.

<sup>28</sup> We will discuss and answer these questions in detail in Chapters 5 and 6. by mmap, the problem of global references could be solved by traditional pointer swizzling built atop mmap, *etc*. We could even combine this with RDMA to gain a DSM model.

Let's first consider the use of mmap to provide an interface for NVM before looking more broadly at persistence in general. The mmap system call attempts to hide storage behind a memory interface through hidden data copies. But, with NVM, these copies are wasteful, and mmap still has significant kernel involvement and the need for explicit msync calls. "Direct Access" (DAX) tries to retrofit mmap for NVM DIMMs by removing the redundant copy, but this *still* fails to address the problem of global context and in-memory data structures for persistent storage. Operating on persistent data through mmap requires the programmer to use either fixed virtual addresses, which presents an infeasible coordination problem as we scale across machines and is fundamentally unportable, or virtual addresses directly, which are ephemeral and require the context of the process that created them<sup>29</sup>.

Attempting to shoehorn NVM programming atop POSIX interfaces (including mmap) results in complexity that arises from combining multiple partial solutions. Given some feature desired by an application, the NVM framework can provide an integrated solution that meshes well with the existing support for persistent data structure manipulation and access, or it can fall-back to POSIX resulting in the programmer needing to understand two different "feature namespaces" and their interactions. An example is naming, where a programmer may need to turn to the filesystem to manage names in a completely orthogonal way to how the NVM framework handles data references. For example, PMDK, an NVM programming library, relies on a filesystem for naming and initial access to persistent memory objects, resulting in different kinds of references, feature sets from filesystems being applied (like security) while others are not (data access), and the complexity of understanding how the PMDK abstractions interact with the POSIX ones. Instead, our model prefers to build legacy support atop new abstractions (as we will see in Section 7.4), and avoid falling back to legacy models for persistent data access.

Even without NVM, we have similar problems. Our goal of programming with memory semantics on in-memory data structures leads to many of the same arguments as above. Additionally, systems that layer new models atop existing interfaces often fail to facilitate effective persistent data sharing and protection. PMDK, for example, makes design choices that limit scalability, since its data objects are not self-contained and do not have a large enough ID space, resulting in the need to coordinate object IDs across machines, a problem we will explore in detail in Chapter 5. For the same reason, although single-address space OSes [19] somewhat address our requirements, they do not consider both requirements at once, nor do they provide an effective and scalable solution to <sup>29</sup> These issues don't even touch the high kernel involvement, in-kernel coordination, and failure-atomicity hazards present when using mmap [29]. long-term data references due to that same coordination complexity (as we will discuss in Section 4.4).

#### 3.3 REMOTE PROCEDURE CALLS

One major aspect of systems programming, particularly in distributed systems, is RPC<sup>30</sup>. We typically use RPC as a mechanism for decomposition in distributed systems, allowing us to break design problems down into smaller, re-usable parts that hide implementation details and are more easily debugged. Decoupling components with RPCs allows them to scale independently—in principle, developers need only agree on a common interface and message format to leverage the benefits of software decoupling. Yet, in reality, RPCs enforce strict interface constraints and often trade adaptability (narrow interfaces are harder to evolve) for simplicity (narrow interfaces limit cross-component interactions), ultimately hampering the goal of scalability.

The chief problem with RPCs is that they are fundamentally locationand compute-centric: RPCs force a programmer to decouple an application by explicitly separating the computational endpoint or *location* where a function is invoked from the location where the function executes. As a consequence, they are well-suited to a relatively narrow set of use cases in which function arguments, which flow from invoker to executor, and returns, which flow back, must be serialized and sent in their entirety, and hence are small, and in which reference data must be located on the executor.

Many scenarios would benefit from decoupling but are simply not feasible using existing RPC mechanisms. For example, the invoking endpoint may have abundant data but limited compute, the invoker may wish to traverse a remote data structure, or the invoker may wish to refer to data that they lack privileges to read. Rapidly growing model sizes, privacy concerns, and the proliferation of last-mile model customizations all exacerbate the issue. To mitigate the problem of location-centric RPCs, data center operators often deploy discovery services, load balancers, or other forms of middleware [40, 59, 72, 112, 121]. These extra indirection layers make the execution endpoint abstract, but at the cost of increased latency and added system complexity. Moreover, we argue that such systems do not address the fundamental problem, which is that *we need a more general mechanism for module composition in distributed systems*.

#### Motivating Example

To illustrate the poor fit of RPC as a decoupling mechanism for some classes of applications, consider the problem of distributed inference for <sup>30</sup> Note that, if you look at Figure 3.1 and squint your eyes, it resembles not just persistence but also communication and data transfer across nodes.

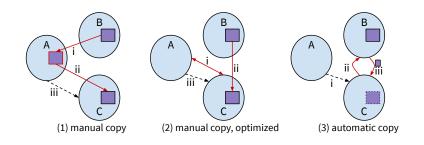

#### FIGURE 3.2

19

Rendezvous of data and compute. Solid red arrows are additional infrastructure-level tasks that are not fundamental to the requested computation.

edge devices. Here, sensors in mobile devices with modest processing and storage resources (*e.g.* mobile phones) are the source of observations used both for training and inference. Recent work has focused on decoupling and distributing machine learning training across edge and cloud resources to minimize client-perceived latency, provide privacy guarantees, and maximize server-side throughput [68, 114].

In this example, we focus on the inference problem that arises in response to device input. Ideally, small models trained in the cloud (via a methodology such as federated learning) are periodically shipped in their entirety to edge devices, which perform local inference. Several trends are upsetting this model. The first is the aggressive growth-roughly  $10 \times$ /year—of models, in particular language models. In 2018, the largest machine translation models at Google were 8.3 billion parameters [113]; a mere two years later, the largest models exceeded 800 billion parameters! Inference on sparse giant models which far exceed device resources must be performed server side, where model serving presents a substantial throughput bottleneck. This is further compounded by last-mile model customization for end users, in which inference tasks for different devices must be performed on slightly different models. As much as 70% of the processing time [30] for these model-serving applications is spent deserializing and loading the sparse personalized models into main memory at request time. Finally, users prefer local models remain local due to confidentiality concerns.

Consider a concrete example (Figure 3.2) that is bedeviled by all of these complexities at once. A mobile device, Alice, in possession of a locally-trained model and an activation, wishes to perform a classification task that requires a partition of a sparse global model, located on cloud resource Bob. Further, imagine that Alice cannot perform the inference locally, either because the global model fragment is too large or because she has inadequate local compute. Finally, imagine that Bob is overloaded, while a separate cloud resource, Carol, is mostly idle.